Package Solution

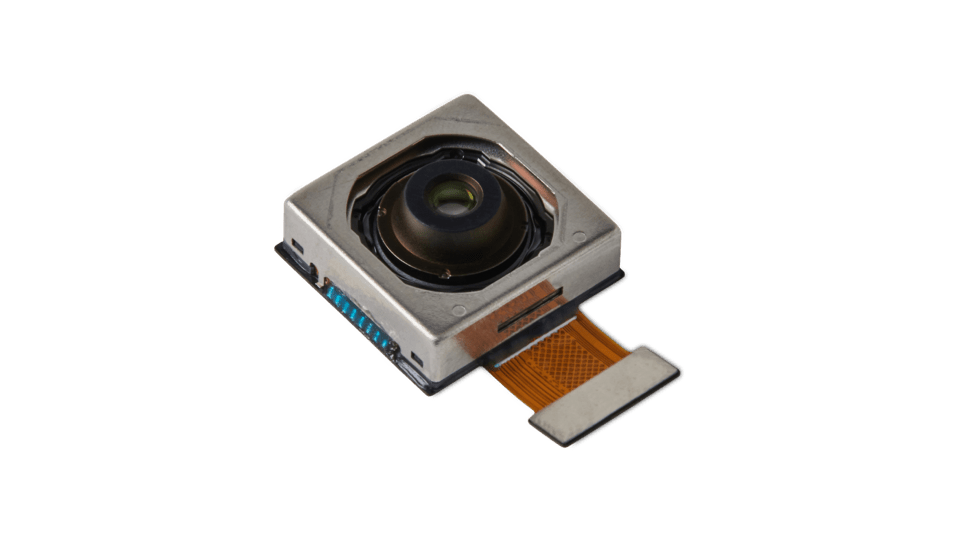

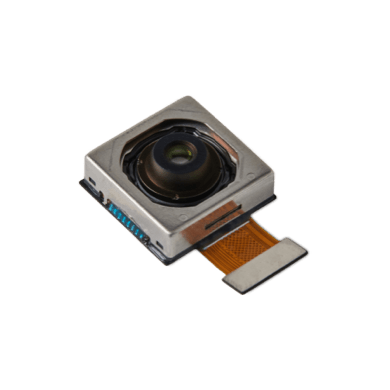

Package Substrate

It is used to transmit electrical signals between the semiconductor and the main board.

It is used in all products that use electricity as a part and is High-density circuit board on which circuits are formed

Tape Substrate

It is thin tape-type substrate that form signal connection between the display Driver-IC and the panel

Display Mask

It is the Photomask for display manufacturing exposure process , and also used as a deposition mask for OLED Pixel implementation